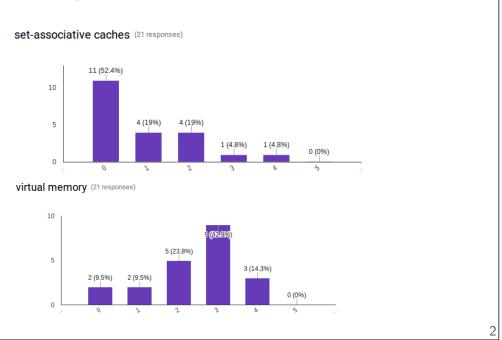

#### Survey results

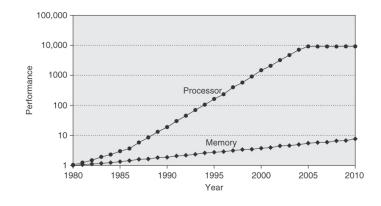

#### **Processor/Memory Gap**

Figure 2.2 Starting with 1980 performance as a baseline, the gap in performance, measured as the difference in the time between processor memory requests (for a single processor or core) and the latency of a DRAM access, is plotted over time. Note that the vertical axis must be on a logarithmic scale to record the size of the processor-DRAM performance gap. The memory baseline is 64 KB DRAM in 1980, with a 1.07 per year performance improvement in latency (see Figure 2.13 on page 99). The processor line assumes a 1.25 improvement per year until 1986, a 1.52 improvement tableween 2000 and 2005, and no change in processor performance (on a per-core basis) between 2005 and 2010; see Figure 1.1 in Chapter 1. Figure: H&P Ch. 2

#### Variety in memory technologies

#### SRAM

approx. 4–6 transitors/bit optimized for speed

#### DRAM

approx. 1 transitor + capacitor/bit optimized for density

..

3

Also smaller  $\implies$  faster

Goal: best performance and best capacity

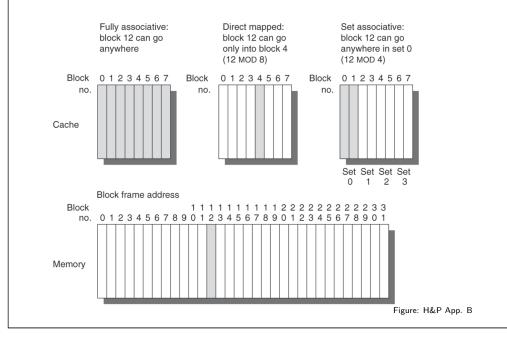

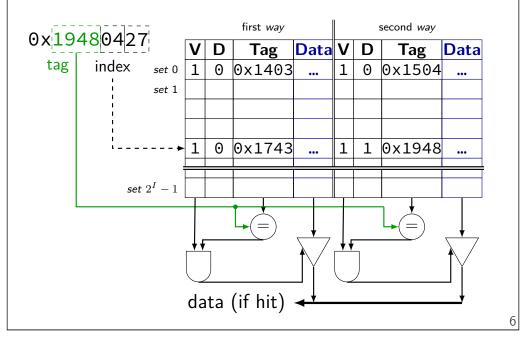

## Associativity

# **Cache Operation**

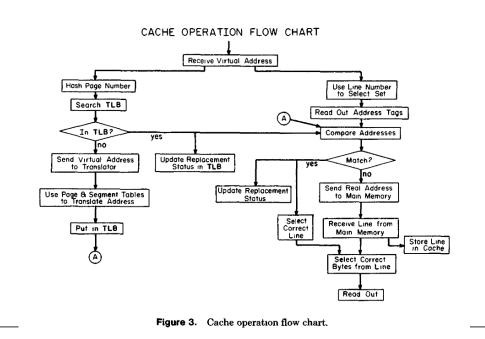

**Cache Flowchart**

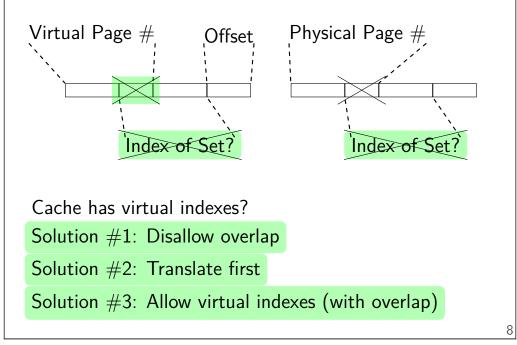

#### **Virtual and Physical**

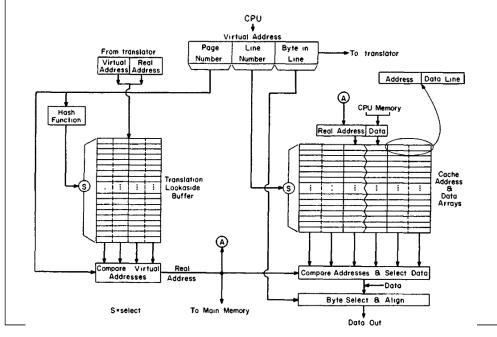

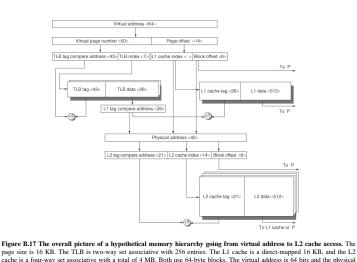

#### Cache and TLB design

Figure 2. A typical cache and TLB design.

## L1: no overlap + L2: translate first

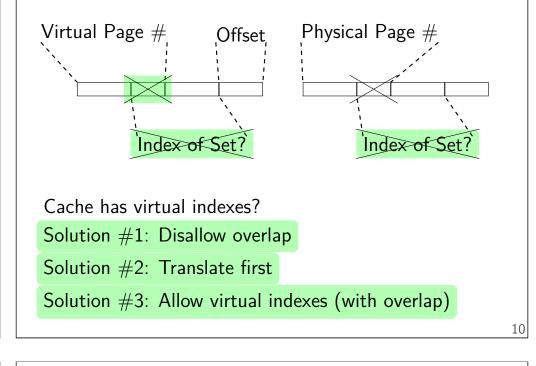

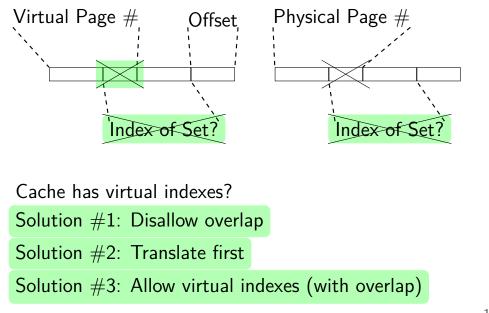

#### Virtual and Physical

## Virtual and Physical

11

address is 40 bits

#### **Virtually Indexed Caches Issues**

do tags store physical or virtual addresses?

what about page table changes?

two virtual addresses (aliasing) for same physical address?

#### **Types of Cache Misses**

compulsory — first access

capacity — not enough space

conflict — enough space, but in wrong sets

(coherency — synchronizing between caches)

14

16

# average memory access time (AMAT)

$\mathsf{AMAT} = \mathsf{hit} \ \mathsf{time} + \mathsf{miss} \ \mathsf{rate} \times \mathsf{miss} \ \mathsf{penalty}$

#### Smith paper summary

Simulation study

Whole bunch of cache parameters

Optimize by applying simulation

| The Smith paper's simulator | miss rate versus AMAT                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------|

| Input?<br>What's missing?   | Every optimization has a complexity cost!<br>Can you figure that out from the paper we read? |

| 17                          | 18                                                                                           |

# miss rate or AMAT versus program performance

How many memory accesses per instruction?

Evenly distributed?

What if all instructions have lots of computation?

What systems that can 'hide' misses with speculation?

#### write stratagies

write-through — write on change

write-back — write on cache eviction also known as copy-back

# replacement policies write buffers random data no longer in cache but not yet in memory fifo need to be checked on reads LRU approximations need to be checked on reads if write-back: write-allocate — bring into cache on write no write-allocate — write-through if not yet in cache 21

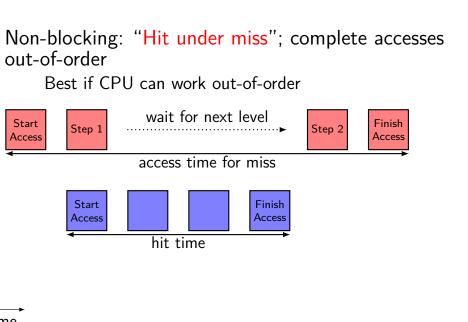

# **Non-blocking**

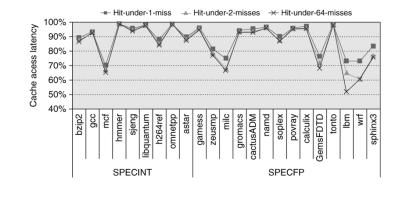

#### **Non-blocking improvement**

Figure 2.5 The effectiveness of a nonblocking cache is evaluated by allowing 1, 2, or 64 hits under a cache miss with 9 SPECINT (on the left) and 9 SPECFP (on the right) benchmarks. The data memory system modeled after the Intel i7 consists of a 32KB L1 cache with a four cycle access latency. The L2 cache (shared with instructions) is 256 KB with a 10 clock cycle access latency. The L3 is 2 MB and a 36-cycle access latency. All the caches are eight-way set associative and have a 64-byte block size. Allowing one hit under miss reduces the miss penalty by 9% for the integer benchmarks and 12.5% for the floating point. Allowing a second hit improves these results to 10% and 16%, and allowing 64 results in little additional improvement

Copyright © 2011, Elsevier Inc. All rights Reserved.

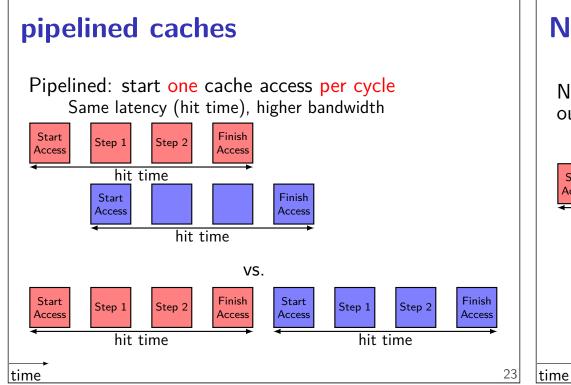

#### **Cache Optimizations**

|                                            | Improves |         |        |       |

|--------------------------------------------|----------|---------|--------|-------|

| Technique                                  | Hit      | Miss    | Hit    | Band- |

|                                            | time     | penalty | ' rate | width |

| Increase block size                        |          | Ν       | Y      |       |

| Increase cache size                        | N        |         | Y      |       |

| Increase associavity                       | Ν        |         | Y      |       |

| Multilevel caches                          |          | Y       |        |       |

| Prioritize reads over writes               |          | Y       |        |       |

| $Virtual\operatorname{-index} = Physical$  | Y        |         |        |       |

| Pipelined cache accesses                   |          |         |        | Υ     |

| Non-blocking caches                        |          | Y       |        | Υ     |

| Prefetching                                |          | Υ       | Υ      |       |

| Way-prediction                             | Y        |         |        |       |

|                                            | I        |         |        |       |

| + complexity costs                         |          |         |        |       |

| (adapted from tables in H&P B and H&P 2.2) |          |         |        |       |

#### **Choice of traces**

#### APPENDIX. EXPLANATION OF TRACE NAMES

- 1. EDC PDP-11 trace of text editor, written in C, compiled with C compiler on PDP-11

- 2. ROFFAS PDP-11 trace of text output and formatting program. (called ROFF or runoff)

- 3. TRACE PDP-11 trace of program tracer itself tracing EDC. (Tracer is written in assembly language.)

- 4. FGO1 FORTRAN Go step, factor analysis (1249 lines, single precision). 12. IEBDG IBM utility that generates

- 5. FGO2 FORTRAN Go step, doubleprecision analysis of satellite information, 2057 lines, FortG compiler.

- 6. FGO3 FORTRAN Go step, double

precision numerical analysis, 840 lines FortG compiler.

- 7. FGO4 FORTRAN Go step, FFT of hole in rotating body. Double-precision FortG.

- 8. CGO1 COBOL Go step, fixed-assets program doing tax transaction selec- 16.

- tion. 9. CGO2 COBOL Go step, "fixed assets:

- year end tax select." 10. CGO3 COBOL Go step, projects de-

- preciation of fixed assets. 11. PGO2 PL/I Go step, does CCW anal-

- vsis.

test data that can be used in program debugging. It will create multiple data sets of whatever form and contents are desired

14. FCOMP FORTRAN compile of program that solves Reynolds partial differential equation (2330 lines).

6

- 15. CCOMP COBOL compile. 240 lines accounting report.

- WATEX Execution of a FORTRAN program compiled using the WATFIV compiler. The program is a combinatorial search routine.

- WATFIV FORTRAN compilation using the WATFIV compiler. (Compiles the program whose trace is the WATEX trace.)

- 18. APL Execution of APL program which does plots at a terminal

- 19. FFT Execution of an FFT program written in ALGOL, compiled using AL-GOLW compiler at Stanford.

#### Mem hierarcht at ISCA'15–16 + **MICRO'15**

SPECcpu x16

"compute-intensive"

NASA Parallel Benchmarks (NPB) x7 "from computational fluid dynamics (CFD)"

#### PARSEC x3

"multithreaded programs"

#### BioBench x3

"a diverse set of bioinformatics applications"

(+ more that appeared less than 3 times + any I missed)

27

25

| Modern cache evaluation tools                                                                                    |   |

|------------------------------------------------------------------------------------------------------------------|---|

| CACTI — "[a]n integrated cache and memory<br>access time, cycle time, area, leakage, and dynamic<br>power model" |   |

| gem5 — "a modular platform for computer-system architecture research"                                            |   |

| Marss86                                                                                                          |   |

| Graphite                                                                                                         |   |

| ESESC                                                                                                            |   |

| Flexus                                                                                                           |   |

| 2                                                                                                                | 9 |

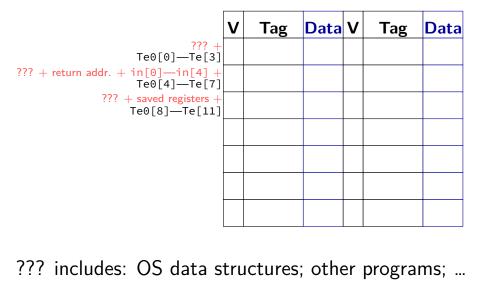

#### S-Box Problem

```

static const u32 Te0[256] = { // 4KB table

0xc66363a5U, 0xf87c7c84U, 0xee777799U, 0xf67b7

0xfff2f20dU, 0xd66b6bbdU, 0xde6f6fb1U, 0x91c5c

0x60303050U, 0x02010103U, 0xce6767a9U, 0x562b2

0xe7fefe19U, 0xb5d7d762U, 0x4dababe6U, 0xec767

// ...

s0 = GETU32(in

) ^ rk[0];

s1 = GETU32(in + 4) ^ rk[1];

s2 = GETU32(in + 8) ^ rk[2];

s3 = GETU32(in + 12) ^ rk[3];

/* round 1: */

t0 = Te0[s0 >> 24] ^ Te1[(s1 >> 16) & 0xff] ^

// ...

rk — round key — TOP SECRET

31

in ____ input ____ accumed known

```

#### **S-Box layout**

varies depending on packet sizes, etc. — change memory layout

#### **DJB's advice for CPU designers**

"document the performance of their chips"

"adding AES support to their instruction sets"

"adding an L1-table-lookup instruction"

"allow [] different action upon return from interrupt"

#### **DJB's advice for AES implementors**

"control the positions of [] variables in memory" after "any uncontrolled code": reload S-box "disabl[ing] hyperthreading" "incorporate ... into the [] kernel" "shift the stack" (relative to S-boxes) make "each load" "take place in a separate cycle" "Every new CPU poses a potential new challenge."

#### **Papers for Next Time**

Jouppi, "Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers", 1990

Cook et al, "A Hardware Evaluation of Cache Partitioning to Improve Utilization and Energy-Efficiency while Preserving Responsiveness", 2013 34