# An Interactive Gate-Level Simulator of a Classical Von Neumann Architecture, as an Educational Aid for Introducing Novices to the Fundamentals of Computer Organization

#### Gabriel Robins

Computer Science Department University of California, Los Angeles Los Angeles, California 90025

#### 1. Abstract

I have developed an interactive tool for the simulation of a classical Von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The simulated system consists of 9 registers, 4 buses, 40 gates, an adder, a memory, a micro-programmed control subsystem, a 3-phase clock, a "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zero-detect logic. A friendly user interface was also implemented, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility. My simulator prototype could effectively be used as an educational tool for the introduction of novices to the fundamentals of computer organization. Alternatively, the construction of such a simulator may in itself constitute a good term project for an upper division hardware course.

<u>Keywords</u>: Computer organization, simulation, learning tools, computer hardware, educational aids, user training systems.

#### 2. Introduction

We have developed an interactive tool for the simulation of a classical von Neumann computer architecture. The simulation takes place at the register, bus, and gate level. The components of our system include 9 registers, 4 buses, 40 gates, 1 adder, a memory, a micro-programmed control subsystem, a 3-phase clock, an extra "scratch" register, logical inverters, a bi-directional shift register, several constant registers, and zerodetect logic. In addition, we have constructed a friendly user interface, featuring an assembler, a microcode interpreter, and a terminal-independent full-screen display facility. There exists a distinct lack of software tools to aid and enhance the teaching of computer science at the undergraduate level. We believe that our interactive simulator prototype constitutes an extremely useful educational tool for the introduction of novices to the fundamentals of computer organization. The architecture we consider is based on the one discussed in [Tanenbaum].

#### 3. Overview

This simulator requires 3 specification: the micro-code, the assembly instruction set, and the user program. When the simulator starts running, it loads the micro-program into the micro-store; next, it reads and assembles the user program into machine language, according to the instruction set specified (or else the default assembly instruction set). The resulting machine program is loaded into the main memory of the simulator. The simulator then begins to execute the micro-program; the micro-program, in turn, fetches, decodes, and executes instructions of the machine-language program.

By programming the simulator in micro-code, the user may thus create new and novel "instruction sets" for the "machine." For example, suppose the user wanted to add an assembly instruction "sqrt" which takes the integer squareroot of the ACC register and leaves the result in the ACC register. The user will then need to add a new opcode called "sqrt" (and a corresponding machine-instruction code) to the assembly instruction set of the machine (by updating that file), and next modify the micro-program to perform the square root operation on the ACC register whenever the new instruction is encountered. The organization of the rest of this paper is as follows: section 4 describes the details of the simulated hardware, section 5 describes the assembler and the assembly language, section 6 describes the microcode interpreter and its language, section 7 discusses the user interface, and section 8 summarizes the implementation and explains how to obtain the source code.

#### 4. The Hardware

The computer system we chose to simulate is a simplified von Neumann-type single-processor micro-program controlled machine. The schematic organization of this system is given in Appendix II. A detailed description of the components and topology of the system follows. Unless otherwise specified, when two registers/buses with different numbers of bits are connected, say m and n where m > n, the connection consists of bits 0 through n-1 of the first register/bus being connected to bits 0 through n-1 of the second register/bus. The rest of the m-n connections are connected to logical low (0).

#### 4.1. Registers

<u>IC</u> - a 10-bit used as the <u>instruction\_counter</u> for the user's program.

**IX** - a 10-bit register used as the <u>index register</u> by user programs for array-type addressing.

<u>SP</u> - a 10-bit register used as a <u>stack pointer</u> for call/return instructions as well as for arbitrary push/pop operations.

$\underline{X}$  - an 18-bit register used as a <u>scratch register</u> in various micro-instructions, and is invisible to the assembly -language program.

ACC - an 18-bit register which serves as an "accumulator" in the user's program.

<u>MAR</u> - a 10-bit register used primarily to store the address of where main memory is going to be written into or read from. It may also be used as a scratch register by the micro-program.

<u>MBR</u> - an 18-bit used to store the data involved in all memory read/write operations.

<u>**OC**</u> - a 6-bit register used to store the <u>op-code</u> of the currently executed macro-instruction.

L - a 2-bit register used to store the indexing/indirection flags of the currently executing assembly instruction.

#### 4.2. Buses

**Data bus** - an 18-bit bi-directional bus that is connected to the various registers and to the adder

output lines. Most movement of data between registers takes place via the data bus.

<u>Address bus</u> - a 10-bit bi-directional bus that is connected to the MAR register and to the adder output bus. This bus is used to supply the MAR register with the address of memory locations in read/write operations.

Left adder bus - an 18-bit bus that connects the various registers and several constant registers with the left input to the adder module.

<u>**Right adder bus</u>** - an 18-bit bus that connects the various registers and several constant registers with the right input to the adder module.</u>

#### 4.3. Gates

There are 40 distinct gates, each, when open, initiates a micro-operation. Any number of gates may be open at the same time, but some combinations of gates are mutually exclusive (ex: left-shift and right-shift). The hardware diagram in Appendix II specifies which gates open what hardware connections.

#### 4.4. Memory

The main memory consists of 1024 words of 18 bits each. The memory locations have addresses in the range 0 through 1023, inclusive. Each word has its bits numbered 0 through 17, inclusive, where bit 0 is considered to be the least significant when numeric values are represented.

#### 4.5. Inverters

There is a single logical inverter between each of the adder left and right buses, and the adder. These may invert none, one, or both arguments to the adder, depending on whether neither, one, or both are enabled.

#### 4.6. Adder

There is an 18-bit adder whose inputs are the outputs of the inverters. At each clock cycle, the adder (which consists of solid-state combinatorial logic) sums its inputs and outputs the answer to its output.

#### 4.7. Shifter

There is a single bi-directional shift register between the adder output and the data and address buses. It may shift the adder output by one bit to either left or right, depending on whether it is enabled.

### 4.8. Zero-detect logic

After each addition operation of the adder, the zero-detect logic resets or presets a bit that can be later tested for branching purposes. The zero-detect logic is set to '1' if the last addition resulted in a zero answer, and to '0' if the last addition resulted in a non-zero answer.

## 4.9. The Control Subsystem

The micro-programmed control subsystem of the machine is implemented by a control store micro-memory, a CSAR (control store address register) and CSBR (control store data register) registers, and hard-wired micro control logic. This entire subsystem is invisible to the assemblylanguage user.

### 4.9.1. The Micro-memory

The micro-memory consists of 512 words of storage, each of which contains 41 bits. The micro-memory words are numbered 0 through 511, inclusive, while the bits in each micro word are numbered 0 through 40, inclusive.

#### 4.9.2. Micro-registers

<u>CSAR</u> - this is a 9-bit register that is used to address the micro-memory. It is similar in function to the MAR register for the main memory. CSAR is an acronym for "Control Store Address Register".

<u>CSBR</u> - this is a 41-bit register that contains the current micro instruction being executed. This register is directly in control of the hard-wired control logic and supervises the opening and closing of control gates (i.e., the generation of control signals) by virtue of the values contained in its bits. CSBR is an acronym for "Control Store Buffer Register".

## 4.9.3. Control Logic

The control logic for the micro programmed control subsystem is hard-wired (in this simulation it is written in C). It supervises the loading of instructions from the micro-memory, incrementing the CSAR register, and generating the control signals from the value of the CSBR and the clock

pulses.

## 4.9.4. Start Toggle

The start toggle is a single bit register that allows the system to commence execution (when high) or causes the entire operation of the system to be suspended (when low). This is used to halt execution of the simulation, so that the user may inspect the contents of various registers/buses.

### 4.9.5. Clock

The operation of the control subsystem is governed by a three-phase clock. The phases of the clock are numbered P0, P1, and P2. The set of 40 system gates is partitioned into 3 distinct nonempty disjoint subsets, each of which contains gates that can be open ONLY during a unique clock phase. These sets are:

<u>phase 1 gates</u> = { 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 37, 38 } <u>phase 1 gates</u> = { 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 39, 40 } <u>phase 3 gates</u> = { 34, 35, 36 }

This partition exists in order to eliminate certain nasty ambiguities that arise when several inputs are allowed to to enter into the same register simultaneously, thereby rendering its contents undefined.

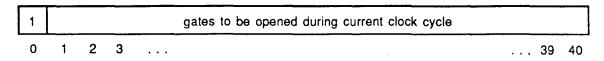

## 4.9.6. Micro-Instruction Format

Each micro instruction has one of the two formats specified in Appendix III. In the first format, the only operations that can occur are gates being opened according to which of bits 1 through 40 of the instruction are set high, during the appropriate clock phases. In the second format, a certain bit (specified by bits 10 through 14) of a register (specified by bits 1 through 9) is examined and compared with bit 15 of that instruction. If the comparison was successful (i.e., they were equal), then micro-control is transferred to the microlocation specified by bits 16 through 25 of the instruction. Both the "bit num" and the "address" fields are encoded in binary; the rest of the fields are linearly encoded, and only one of the bits of all of these fields must be set high (the rest being set low) in order for the instruction to logically make senseí.

Having the system be micro-programmed

makes it very powerful with respect to non-microprogrammed systems. This is because new userlevel assembly instruction sets can be easily implemented, and only by changing the microprogram, not having to touch the hardware at all. In fact, users may write their own microprograms, thereby taking advantage of higher machine efficiency to suit their particular applications.

### 5. The Assembly Language

This section describes the assembler for the machine. The purpose of the assembler is to "compile" the user's assembly language into machine language and to place the resulting object code into the main memory so that it may be later executed. The reason for having an assembler, is to make the task of programming less tedious for the user; otherwise, the user would have had to program directly in the hardware's binary machine language.

A reasonable instruction set has already been written (and is the default instruction set) in order to accommodate users who do not wish to go through the tedium of writing their own microprograms. Sensible mnemonics were also assigned to the various operations. It should be noted that the assembler is written in a general manner. The opcode mnemonics are read from an external file, and thus subject to modification by the user. The rest of the functions of the assembler remain unchanged from language to language. In fact, the only difference between two assembly languages here is between their two respective opcode mnemonic sets. Appendix IV gives the the mnemonics and their respective opcodes for the default assembly instruction set.

#### 5.1. Stack

As can be easily seen, this language has a built-in stack facility for calling functions and for pushing values onto a stack. This makes the language posses substantial versatility. In the micro-program, the stack is rooted at the top of memory (location 1023) and grows toward smaller memory locations.

#### 5.2. Instruction Format

The instruction format for this language calls for each infstruction to be one word in length, in the format specified in Appendix V.

### 5.3. Assembly Syntax

This assembler recognizes an assembly language that is in a standard format, where each line of code is composed of one to three fields: label, opcode, and address. The address field may be immediately preceded by the character "" which signified indirection, and succeeded by the two characters '()' which signify indexing. In addition to the default opcodes described earlier, there are three additional pseudo-opcode: the 'equ' opcode, which is used to associate a label with a number/address, the 'con' pseudo-operator, which is used to store data/constants into memory locations during the assembly process, and the 'org' pseudo-operator, used to assemble code into several separate memory regions. A sample assembly program is given in Appendix I.

#### 6. The Microcode Interpreter

This section describes the microcode interpreter. The function of the microcode interpreter is to convert the microcode from the symbolic form it is written in, to the form that can be placed into the micro-memory. Alternatively, the microcode would have been coded in binary by the user, which makes for a very tedious and error-prone task.

#### 6.1. Microcode Syntax

The micro-program in symbolic form is composed of as many occurrences of the following 40 strings as desired: alu-right=ic, alu-left=ic, alu-right=ix, alu-left=ix, alu-right=sp, aluleft=sp, alu-right=x, alu-left=x, alu-right=acc, alu-left=acc, alu-right=-1, alu-left=0, aluright=0, alu-right=1, alu-right=sign, mar=mbr, oc=mbr, ii=mbr, alu-left=mbr, left-shift, rightshift, data-bus=alu-output, address-bus=aluoutput, data-bus=mbr, sp=data-bus, x=data-bus, x=18, acc=data-bus, mar=ic, ic=data-bus, mar=address-bus, mbr=data-bus, ix=data-bus. mbr=mem(mar), mem(mar)=mbr, start=off, invert-left-alu, invert-right-alu, x=10, databus=mar.

Each set of micro-operations that are specified on ONE input line, will be executed during ONE clock cycle (but maybe in different clock phases). The character ';' is used as a separator and should follow each one of the strings. Labels may be used, and comments are placed between curly brackets. In addition to the micro operations specified above, two more micro-instructions may be specified: the '<u>if</u>' and the '<u>goto</u>'. The 'if' has the following syntax:

#### if(reg,bit)=cmp then goto label;

where '<u>reg</u>' is one of the strings { ic, ix, sp, x, acc, mbr, mar, oc, ii, zero-detect }, '<u>bit</u>' is a decimal number that represents the bit to be tested, '<u>cmp</u>' is either 0 or 1 (the value to be tested against), and '<u>label</u>' is a valid label in the micro-program to be branched to if the test is successful (i.e. reg(bit)=cmp ). The 'goto' microinstruction is much simpler:

#### goto label;

This micro-instruction unconditionally transfers micro-control to the micro-location specified by 'label'.

#### 7. The User Interface

#### 7.1. Screen format

The simulator updates the terminal display in a screen-oriented fashion. Direct cursor control is exercised through a library package which is intelligent enough to look up the terminal type in the appropriate UNIX system file. The most current values of the various registers and buses are displayed on the screen at all times, unless the user specified to the simulator to run in the 'quiet' mode. This display makes possible for the user to trace only the specific system components of his/her choice, while possibly ignoring the rest, with minimal cognitive overhead. While the system is running, the display appears as in Appendix VI.

#### 7.2. The interaction With the User

All commands are one letter long, which in all cases is the first letter of the word describing the command. A short menu is present at the bottom of the display at all times, summarizing the commands. A help facility makes it possible to review the functions of the commands at any given time. Some commands generate a sub-menu, which contains subcommands appropriate for the original command only.

The various commands that are available at the top-lewel are: <u>Pause</u> - pauses between clock cycles (or phases), and wait for a new command, <u>Continue</u> - negates the last pause command, <u>Stop</u> - halts the machine, and creates a final memory dump, <u>Quiet</u> - does all things silently without updating the display, <u>Trace</u> - negates the 'quiet' command, <u>Redraw</u> - clears the screen and redraw the display, <u>Values</u> - allows the user to change the contents of registers and buses, <u>Microcode</u> - lists the interpreted microcode, <u>Object</u> - lists the object code of the assembled program, <u>Examine</u> - lists the contents of the entire main memory, <u>Help</u> - print this summary.

### 7.3. Error Handling

The microcode interpreter, as well as the assembler, may produce various diagnostic messages during normal operation. This usually occurs when the user fails to comply with the syntax rules built into the simulator. All such error messages are meant to be self-explanatory. The line number on which the error occurred is included in the error-message, when appropriate. When the microcode contains errors, assembly will not be attempted. When the source program contains errors, execution will not be attempted.

## 8. The Implementation

The hard-wired part of the control subsystem is written directly in the C language (after all, the simulation has to *end* somewhere). Execution of the microcode is done here and here only. Execution of the microcode commences at micro location 0 and proceeds logically unless "goto" instructions alter the logic flow. The Microcode is assumed to have been assembled and placed into the micro-memory. Execution of the microcode halts only after the microcode instruction 'start=off' has been executed. Each microcode instruction is fetched from the micro-memory, placed into the CSBR register, and combined with the clock pulses to generate control signals that will open various system gates.

As the microcode executes, it will fetch and interpret individual assembly/machine instructions from the user's program in main memory. Appropriate gates will open and close, and the desired effect will be achieved by having the corresponding micro operations take place. The types and effects of the various micro operations are described in earlier sections. To obtain the annotated C-sources constituting the simulator, please contact the author: Gabriel Robins, P.O. Box 8369, Van Nuys, California, 91409-8369, U.S.A.

#### 9. Summary

I have developed an interactive tool for the simulation of a classical Von Neumann computer architecture. The simulation takes place at the register, bus, and gate level, and features a friendly user interface, an assembler, a microcode interpreter, and a terminal-independent full-screen display facility.

There exists a distinct lack of software tools to aid the teaching of computer science at the undergraduate level. I believe that my interactive simulator prototype, or other similar tools, will prove to be useful educational tools for the introduction of novices to the fundamentals of computer organization. Indeed, the construction of such a simulator will in itself constitute a good term project for an upper division hardware course.

#### 10. Bibliography

Tanenbaum, S., <u>Structured Computer Organization</u>, Englewood Cliffs, New Jersey, Prentice Hall, 1976.

#### **11.** Appendix I: Usage Examples

#### 11.1. Sample Micro-program

This is part of the default microcode for the simulated machine:

```

{ initialize the instruction counter and stack pointer to 0 }

alu-left=0 ; alu-right=0 ; data-bus=alu-output ; ic=data-bus; sp=data-bus;

{ fetch a macro-instruction from the main memory }

mar=ic; mbr=mem(mar);

fetch:

{ transfer the opcode and the indexing and indirection flags and

increment the instruction counter }

oc=mbr; ii=mbr; mar=mbr; alu-left=ic; alu-right=1; data-bus=alu-output; $

ic=data-bus;

{ the following section is a giant 'switch' construct, that decodes the 64

possible opcodes and branches to the appropriate place for the execution

of the corresponding machine instruction }

0-to-63: if bit(oc, 5)=1 then goto 32-to-63;

0-to-31: if bit(oc, 4)=1 then goto 16-to-31;

0-to-15: if bit(oc,3)=1 then goto 8-to-15;

0-to-7: if bit(oc,2)=1 then goto 4-to-7;

0-to-3: if bit(oc,1)=1 then goto 2-to-3;

0-to-1: if bit (oc, 0)=1 then goto 1-to-1;

{ nop - no operation }

0-to-0: goto fetch;

{-------

{ add - add memory to register }

{------

_____}

{ see if this instruction requires indexing }

1-to-1: if bit(ii,0)=0 then goto 1-to-1-no-indexing;

{ preform the indexing }

data-bus=mar; x=data-bus;

alu-right=ix; alu-left=x; address-bus=alu-output; mar=address-bus;

{ see if this instruction requires indirection }

1-to-1-no-indexing: if bit(ii,1)=0 then goto 1-to-1-no-indirection;

{ perform the indirection }

mbr=mem(mar);

mar=mbr;

{ fetch the data from memory }

1-to-1-no-indirection: mbr=mem(mar);

alu-left=mbr; alu-right=acc; data-bus=alu-output; acc=data-bus;

goto fetch;

2-to-3: if bit(oc,0)=1 then goto 3-to-3;

```

{-----} { sub - subtract memory from register } {------{ see if this instruction requires indexing } 2-to-2: if bit(ii,0)=0 then goto 2-to-2-no-indexing; { preform the indexing } data-bus=mar; x=data-bus; alu-right=ix; alu-left=x; address-bus=alu-output; mar=address-bus; { see if this instruction requires indirection } 2-to-2-no-indexing: if bit(ii,1)=0 then goto 2-to-2-no-indirection; { perform the indirection } mbr=mem(mar); mar=mbr; { fetch the data from memory } 2-to-2-no-indirection: mbr=mem(mar); alu-left=mbr; alu-right=0; invert-left-alu; data-bus=alu-output; x=data-bus; alu-left=x; alu-right=1; data-bus=alu-output; x=data-bus; alu-left=x; alu-right=acc; data-bus=alu-output; acc=data-bus; goto fetch; { Most of the micro-program is omitted here for space considerations...} { hlt - halt the machine } {-----} 63-to-63: start=off; goto fetch; end

11.2. Sample Assembly Program

{ This program generates the first 25 Fibonacci numbers and places them in an array in memory locations 50 thru 74 }

| max<br>array<br>acc<br>ix | equ 25<br>equ 50<br>equ 0<br>equ 2<br>call init                                             | <pre>{ number of Fibonacci numbers we want } { array begins at 50 } { defines the accumulator } { defines the index register } { initialize }</pre>                                                                                                                                                        |

|---------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fibo                      | incr ix<br>ldai array<br>addai max<br>subar ix<br>janz fibo<br>hlt<br>org 100               | <pre>{ get the Nth-2 Fibonacci number } { add to it the Nth-1 Fibonacci number } { store the result into the array } { increment the index } {} {} {} { see if we have enough Fibonacci nums } {} { if not, go generate some more } { stop the machine } { place the routine starting at loc 100 } }</pre> |

| init                      | ldai array<br>ldixr acc<br>ldai 1<br>sta 0()<br>incr ix<br>sta 0()<br>incr ix<br>ret<br>end | <pre>{ initialize the array index } { set the 1st Fibonacci number manually } { set the 2nd Fibonacci number manually } { set the array pointer to the 3rd element } { return to the caller } { end of assembly }</pre>                                                                                    |

## 11.3. Main Memory Dump

Note the computed Fibonacci numbers beginning in memory location 50:

| I  | Location: | 0 =     | 000000000      | Contents:    | 10000000001100100 = 131172            |

|----|-----------|---------|----------------|--------------|---------------------------------------|

| I  | Location: |         | 0000000001     | Contents:    | 00001101111111110 = 14334             |

| I  | location: | 2 =     | 000000010      | Contents:    | 00000101111111111 = 6143              |

| I  | location: | 3 =     | 000000011      | Contents:    | 00010001000000000 = 17408             |

| I  | location: |         | 0000000100     | Contents:    | 00010100000000010 = 20482             |

| L  | location: | 5 =     | 000000101      | Contents:    | 100101000000110010 = 151602           |

| L  | location: | 6 =     | 0000000110     | Contents:    | 00011100000011001 = 28697             |

| L  | ocation:  | 7 =     | 000000111      | Contents:    | 00111000000000000 = 57346             |

| L  | location: | 8 =     | 0000001000     | Contents:    | 01110100000000001 = 118785            |

| L  | ocation:  | 9 =     | 0000001001     | Contents:    | 1111110000000000 = 258048             |

| L  | ocation:  | 10 =    | 0000001010     | Contents:    | 0000000000000000000 = 0               |

|    | (inter    | nediate | locations have | the same val | Lue)                                  |

| L  | location: |         | 0000110001     |              | 0000000000000000000 = 0               |

| L  | ocation:  | 50 =    | 0000110010     | Contents:    | 000000000000000001 = 1                |

| L  | ocation:  | 51 =    | 0000110011     | Contents:    | 000000000000000001 = 1                |

| L  | ocation:  | .52 =   | 0000110100     | Contents:    | 000000000000000000000000000000000000  |

| L  | ocation:  | 53 =    | 0000110101     | Contents:    |                                       |

| L  | ocation:  | 54 =    | 0000110110     | Contents:    | 000000000000000101 = 5                |

|    | ocation:  |         | 0000110111     | Contents:    | 000000000000000000000000000000000000  |

|    | ocation:  |         | 0000111000     | Contents:    | 00000000000001101 = 13                |

|    | ocation:  |         | 0000111001     | Contents:    | 000000000000010101 = 21               |

|    | ocation:  |         | 0000111010     | Contents:    | 000000000000100010 = 34               |

|    | ocation:  |         | 0000111011     | Contents:    | 00000000000110111 = 55                |

|    | ocation:  |         | 0000111100     | Contents:    | 00000000001011001 = 89                |

|    | ocation:  |         | 0000111101     | Contents:    | 00000000010010000 = 144               |

|    | ocation:  |         | 0000111110     | Contents:    | 00000000011101001 = 233               |

|    | ocation:  |         | 0000111111     | Contents:    | 00000000101111001 = 377               |

|    | ocation:  |         | 0001000000     | Contents:    | 00000001001100010 = 610               |

|    | ocation:  |         | 0001000001     | Contents:    | 00000001111011011 = 987               |

|    | ocation:  |         | 0001000010     | Contents:    | 00000011000111101 = 1597              |

|    | ocation:  |         | 0001000011     | Contents:    |                                       |

|    | ocation:  |         | 0001000100     | Contents:    |                                       |

|    | ocation:  |         | 0001000101     | Contents:    | 000001101001101101 = 6765             |

|    | ocation:  |         | 0001000110     | Contents:    |                                       |

|    |           |         | locations have |              |                                       |

| T, | ocation:  |         | 0001100011     | Contents:    |                                       |

|    | ocation:  |         | 0001100100     | Contents:    | 100101000000110010 = 151602           |

|    | ocation:  |         | 0001100101     | Contents:    | 01001000000000000 = 73728             |

|    | ocation:  |         | 0001100110     | Contents:    | 1001010000000000000000000000000000000 |

|    | ocation:  |         | 0001100111     | Contents:    | 0001000100000000000000000000000000000 |

|    | ocation:  |         | 0001101000     | Contents:    | 0001010000000000000000000000000000000 |

|    | ocation:  |         | 0001101000     |              | 0001000000000000000000000000000000000 |

|    | ocation:  |         | 0001101010     |              | 0001010000000000000000000000000000000 |

|    | ocation:  |         | 0001101010     |              | 1000101000000000000000000000000000000 |

|    |           |         |                |              |                                       |

| Ŀ  | ocation:  |         | 0001101100     |              | 000000000000000000 = 0                |

| -  | •         |         | locations have |              | •                                     |

|    |           |         | 1111111110     |              | 00000000000000000 = 0                 |

| ىك | ocation:  | 1023 =  | 1111111111     | Contents:    | 00000000000000001 = 1                 |

|    |           |         |                |              |                                       |

## 12. Appendix II: The Hardware Diagram

÷

## **13. Appendix III: The Microcode Instruction Format**

### (I) The **GATE** micro-instruction:

•

(II) The **TEST** micro-instruction:

| 0 | IC | IX | SP | Х | ACC | MBR | MAR | 8 |   | bit num | cmp | address | zd | unused |

|---|----|----|----|---|-----|-----|-----|---|---|---------|-----|---------|----|--------|

| 0 | 1  | 2  | 3  | 4 | 5   | 6   | 7   | 8 | 9 | 1014    | 15  | 1625    | 26 | 2740   |

## 14. Appendix IV: The Default Assembly Instruction Set

| <br>op num | mnemonic | binary code | effect of operation                  |

|------------|----------|-------------|--------------------------------------|

| 0          | nop      | 000000      | no operation                         |

| <br>1      | add      | 000001      | add memory to register acc           |

| 2          | sub      | 000010      | subtract memory from register acc    |

| 3          | lda      | 000011      | load memory into register acc        |

| 4          | sta      | 000100      | store register acc into memory       |

| 5          | incr     | 000101      | increment register                   |

| 6          | decr     | 000110      | decrement register                   |

| 7          | addai    | 000111      | add to register acc immediate        |

| 8          | subai    | 001000      | subtract from register acc immediate |

| 9          | addixi   | 001001      | add to ix immediate                  |

| 10         | subixi   | 001010      | subtract from ix immediate           |

| 11         | addspi   | 001011      | add to sp immediate                  |

| 12         | subspi   | 001100      | subtract from sp immediate           |

| 13         | addar    | 001101      | add register to acc                  |

| 14         | subar    | 001110      | subtract register from acc           |

| 15         | addixr   | 001111      | add register to ix                   |

| 16         | subixr   | 010000      | subtract register from ix            |

| 17         | ldar     | 010001      | load acc with register               |

| 18         | ldixr    | 010010      | load ix with register                |

| 19         | Idicr    | 010011      | load ic with register                |

| 20         | inva     | 010100      | invert acc                           |

| 21         | invix    | 010101      | invert ix                            |

| 22         | anda     | 010110      | and acc with memory                  |

| 23         | ora      | 010111      | or acc with memory                   |

| 24         | xora     | 011000      | xor acc with memory                  |

| 25         | rsfta    | 011001      | right shift acc                      |

| 26         | Isfta    | 011010      | left shift acc                       |

| 27         | jmp      | 011011      | jump                                 |

| 28         | jaz      | 011100      | jump if acc is zero                  |

| 29         | janz     | 011101      | jump if acc is not zero              |

| 30         | jixz     | 011110      | jump if ix is zero                   |

| 31         | jixnz    | 011111      | jump if ix is not zero               |

| 32         | call     | 100000      | call a subroutine                    |

| 33         | ret      | 100001      | return to caller                     |

| 34°        | pusha    | 100010      | push register acc onto stack         |

| 35         | popa     | 100011      | pop acc from stack                   |

| 36 | zeroa | 100100 | zero out the acc   |

|----|-------|--------|--------------------|

| 37 | Idai  | 100101 | load acc immediate |

| 63 | hlt   | 111111 | halt the machine   |

.

# 15. Appendix V: The Assembly Instruction Format

| operation code | indirection | indexing | address of operand |   |

|----------------|-------------|----------|--------------------|---|

| 17 12          | 11          | 10       | 9 0                | - |

Bit 11, when on, causes indirection to occur. Bit 10, when on, causes indexing to occur via the IX register. Indexing takes precedence over indirection.

## 16. Appendix VI: The Main Display

••• \*\* ,

| Computer-Simulation-by          | Gabriel-Robins                                                                | -version-3-of-7/26/88         |  |  |

|---------------------------------|-------------------------------------------------------------------------------|-------------------------------|--|--|

| ACC=000100010100101111=17711    | DATA-BUS=0                                                                    | 0000000000000000=0            |  |  |

| MBR=0001000100000000000=17408   | RDDRESS-BUS=0000000000=0<br>RLU-LEFT-BUS=000000000000000000000000000000000000 |                               |  |  |

| MAR=00000000000                 |                                                                               |                               |  |  |

| I C=0000000011=3                |                                                                               |                               |  |  |

| open gates: 2 14 16 17 18       |                                                                               |                               |  |  |

| micro-ops: alu-left=ic; alu-r   | right=1; mar=mbr; oc=mbr; ii=mbr;                                             |                               |  |  |

|                                 |                                                                               | CLOCK-PHASE=0                 |  |  |

| 0C=000100=4   =01=1             | Micro Program<br>Control Logic                                                | START=off pausing             |  |  |

| CSAR=000000011=3                |                                                                               | SP=000000000=0                |  |  |

| CSBR=1010000000000010111000100  | 0000010000000000                                                              | IX=0001000111=71              |  |  |

| X=000000011111111111=1023       | type=GRTE                                                                     |                               |  |  |

| -Pause-Continue-Stop-Quiet-Trac | e-Redraw-Values-Mi                                                            | i crocode-Object-Examine-Help |  |  |

## 17. Table of Contents

.

| 1Abstract                                            | 1 |

|------------------------------------------------------|---|

| 2Introduction                                        | 1 |

| 3Overview                                            | 1 |

| 4The Hardware                                        | 2 |

| 4.1Registers                                         | 2 |

| 4.2Buses                                             | 2 |

| 4.3Gates                                             |   |

| 4.4Memory                                            | 2 |

| 4.5Inverters                                         | 2 |

| 4.6Adder                                             |   |

| 4.7Shifter                                           | 2 |

| 4.8Zero-detect logic                                 |   |

| 4.9The Control Subsystem                             |   |

| 4.9.1The Micro-memory                                | 3 |

| 4.9.2Micro-registers                                 |   |

| 4.9.3Control Logic                                   |   |

| 4.9.4Start Toggle                                    |   |

| 4.9.5Clock                                           |   |

| 4.9.6Micro-Instruction Format                        | 3 |

| 5The Assembly Language                               | 4 |

| 5.1Stack                                             |   |

| 5.2Instruction Format                                | 4 |

| 5.3Assembly Syntax                                   | 4 |

| 6The Microcode Interpreter                           | 4 |

| 6.1Microcode Syntax                                  | 4 |

| 7The User Interface                                  |   |

| 7.1Screen format                                     | 5 |

| 7.2The interaction With the User                     |   |

| 7.3Error Handling                                    | 5 |

| 8The Implementation                                  | 5 |

| 9Summary                                             | 6 |

| 10Bibliography                                       | 6 |

| 11Appendix I: Usage Examples                         | 6 |

| 11.1Sample Micro-program                             | 6 |

| 11.2Sample Assembly Program                          | 7 |

| 11.3Main Memory Dump                                 | 8 |

| 12Appendix II: The Hardware Diagram                  | 8 |

| 13Appendix III: The Microcode Instruction Format1    | 0 |

| 14Appendix IV: The Default Assembly Instruction Set1 | 0 |

| 15Appendix V: The Assembly Instruction Format1       | 1 |

| 16Appendix VI: The Main Display1                     | 1 |

| <br>17Table of Contents1                             | 2 |

• •